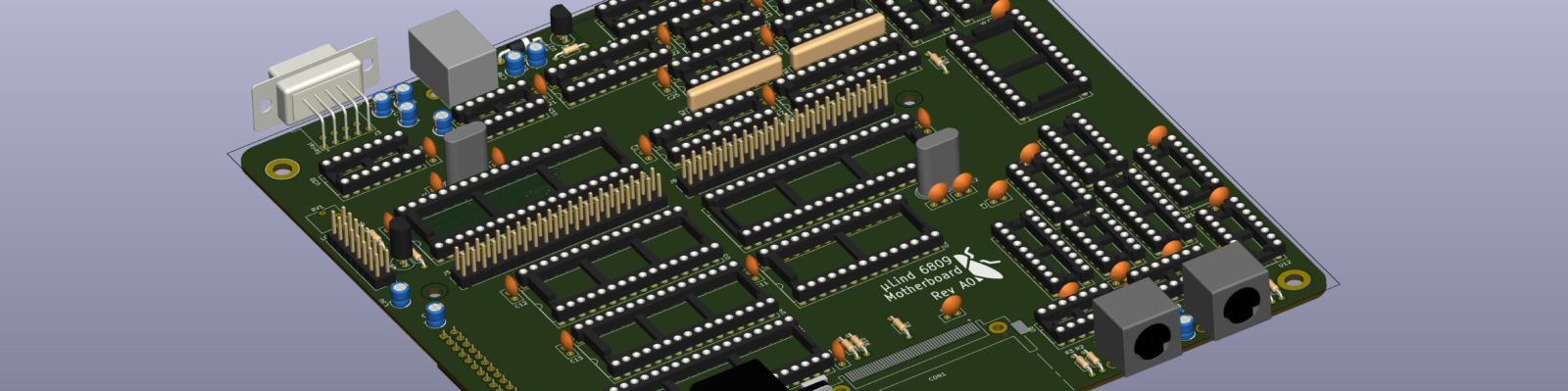

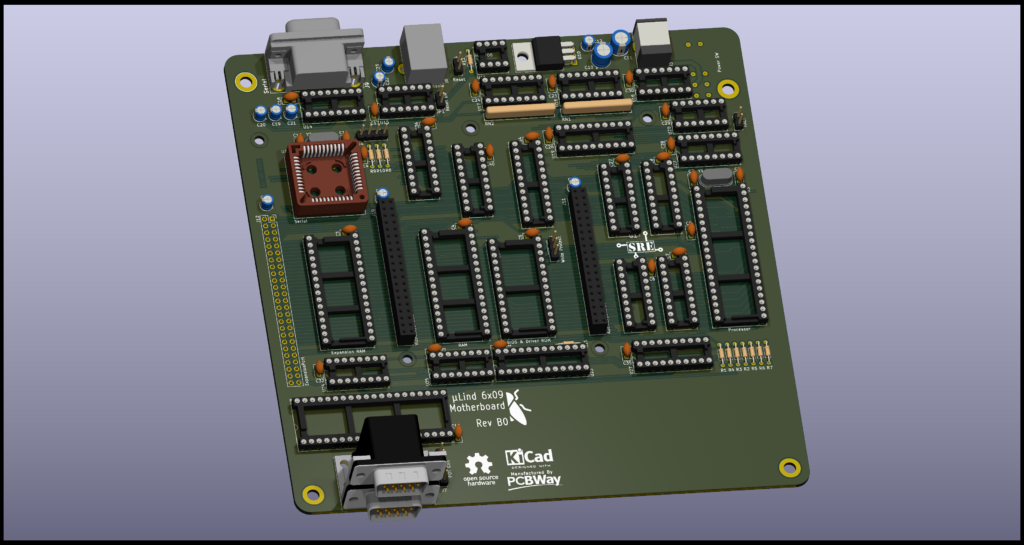

In this stage we will add following features:

- A 65c22 based parallell port used for two C64 compatible joystick ports.

There might be something for the shift register port on it later on… - A fully developed interrupt handler, with priority based interrupts and a register to R/W a filter for interrupts, so we can limit possible interrups during specific task but still be able to recieve some.

- A complete address decoder with a R/W 4-bank system, allowing us to utilize up to 4 MB RAM.

There will be sockets for 2 512kB RAM chips on the motherboard. The rest will be available on the expansion port. - 3 addressable expansion heders, one dedicated 40 pin header dedicated for a graphics card, one 40 pin header dedicated for a audio card (with separate enable signals for left and right) and one 50 pin header on the bottom side, an true expansion port, with full address access, bus request signals (to be able to implement some fancy DMA expansion boards later) and signals to control address translation system (To be able to utilize the 3 MB extra RAM).

The final parts that will come in stage 3 will be (if nothing changes when we try the stage 2 board out):

- A Compact Flash interface, to be able to store data and read programs from.

- A PS2 interface for both keyboard and mouse.

| Firmware Files | Coming later… |

| Schematics | Schematics |

| Model | STEP |

| Gerber | Gerber |

I have also created a BOM for Stage 2:

| ID | Desc | PartNr | Count |

|---|---|---|---|

| U3 | Processor | HD6309 | 1 |

| U7, U9 | SRAM 512k | AS6C4008 | 1 |

| U5 | EEPROM 8k | 28C64 | 1 |

| U2, U4, U6, U28 | Bus Trcv | 74AHCT245 | 4 |

| U13 | Serial Controller | xr88c92 | 1 |

| U14 | Serial Trcv | Max232 | 1 |

| U15 | USB Trcv | MCP2221 | 1 |

| Y1 | Crystal 8MHz | 1 | |

| U9 | LED register | 74AHCT373 | 1 |

| U10 | Regulator | BA05CCOT | 1 |

| U11 | Reset generator | MAX708 | 1 |

| J3 | Power Jack | 1 | |

| SW1 | Power Switch | C128 Power Switch | 1 |

| U12 | Parallell Controller | R6522 | 1 |

| Joy1 | Joystick Ports | DB9-2 | 1 |

| J8 | USB B port | USB-B | 1 |

| J9 | Serial Port | DB9 | 1 |

| Y2 | Serial Crystall | 3.3864 MHz | 1 |

| U17, U18 | IRQ Decoder | 74AHCT148 | 2 |

| U19, U21 | IRQ Bus Trcv | 74AHCT574 | 2 |

| U22 | IRQ Generator | 74AHCT85 | 1 |

| U20 | NAND | 74AHCT00 | 1 |

| U16 | NOR | 74AHCT02 | 1 |

| U23, U26 | Logic | ATF22v10 | 2 |

| U27 | Logic | ATF16v8 | 1 |

| U24, U25 | Register 4×4 | 74AHCT670 | 2 |

| J10, J11 | Connector | 2×20 | 2 |

| J12 | Connector | 2×25 | 1 |

| C3-C9, C36, C13, C14, C17, C18, C24-C35, C40 | Decoupling caps | 100nF | 25 |

| C1, C2 | Processor osc cap. | 22pF | 2 |

| C19-C23 | Serial charge cap. | 1µF | 5 |

| C15, C16 | Serial osc cap. | 43pF | 2 |

| C12, C37-C39 | Power filter | 10µF | 4 |

| C11 | Power filter | 100µF | 1 |

| C10 | Power filter | 33µF | 1 |

| R1-R7, R11, R12 | Pull-ups/downs | 4k7 Ohm | 9 |

| R8 | B current limiter | 1k Ohm | 1 |

| R9 | G current limiter | 330 Ohm | 1 |

| R10 | R current limiter | 560 Ohm | 1 |

| RN1, RN2 | IRQ Pull-ups | 8x 4k7 Ohm | 2 |